Посещение руководством крупных компаний своих филиалов по всему свету в эпоху господства всепроникающих социальных сетей предоставляет большое количество дополнительной информации, непроизвольно «слитой» даже достаточно опытными специалистами. Размещая фотографии своих инспекционных путешествий, высшие менеджеры зачастую публикуют информацию о технологиях следующего поколения, еще не раскрытую компанией официально.

Характерный случай произошел во время поездки исполнительного вице-президента и генерального директора Intel Client Computing Group Грегори Брайанта в исследовательский центр Intel в Израиле. Пост одного из высших менеджеров Intel в Twitter раскрыл некоторую информацию о будущей технологии Thunderbolt 5, которая до настоящего времени не разглашалась широкой публике.

Начиналось все с простого поста, содержащего 4 фотографии о первом дне в Израиле и посещении лабораторий исследовательского центра. Однако в один из кадров попал плакат на стене лаборатории, текст которого раскрывает «технологию 80G PHY». Фотография была быстро удалена, и теперь все желающие могут увидеть на странице Грегори Брайанта с рассказом о первом дне в Израиле только три фото. Тем не менее след в интернете остался, и эксперты принялись обсуждать детали непроизвольно раскрытой технологии.

Из заглавной строки плаката становится ясно, что Intel работает на физическом уровне (PHY) для соединений со скоростью 80 Гбит/с, что в два раза превосходит скорость стандарта Thunderbolt 4. Во второй строке указывается, что «USB 80G предназначен для поддержки существующей экосистемы USB-C», а это означает, что при сохранении существующего разъема USB-C компания Intel планирует удвоить скорость передачи информации.

В дальнейшем представлена специфическая техническая информация, более интересная узконаправленным специалистам. В частности, в третьей строке сообщается, что «PHY будет основан на новой технологии модуляции PAM-3». Это раскрывает процесс передачи «0» и «1», который традиционно осуществляется при помощи кодирования NRZ, позволяющего передать один бит информации, «0» или «1».

Амплитудно-импульсная модуляция PAM-4 позволяет передавать по 2 бита, а цифра 4 показывает различные варианты передачи данных: «00», «01», «10», «11». Таким образом PAM-4 при той же частоте имеет в 2 раза большую полосу пропускания, чем соединение NRZ. Между тем технология PAM-3 позволяет передавать данные формата «-1», «0» или «+1». Система фактически объединяет две передачи PAM-3 в 3-битный сигнал данных, например 000 — это -1, за которым следует -1. Для большей наглядности кодирования PAM-3 имеется специальная таблица.

При сравнении трех систем кодирования становится ясно, что PAM-3 находится между NRZ и PAM-4. Выбор Intel системы PAM-3 основан на том, что при более высокой пропускной способности, чем NRZ, не требуется дополнительных ограничений, необходимых при подключении PAM-4.

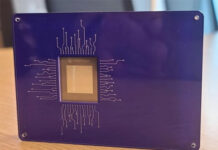

В следующей строке описан таинственный «тестовый чип N6, ориентированный на новую технологию PHY» и демонстрирующий «многообещающий результат».